## EC6504 MICROPROCESSOR AND MICROCONTROLLER

#### ANNA UNIVERSITY, CHENNAI-25 SYLLABUS COPY REGULATION 2013

#### EC6504 MICROPROCESSOR AND MICROCONTROLLER

LTPC 3 0 03

#### **UNIT I THE 8086 MICROPROCESSOR**

9

$Introduction\ to\ 8086-Microprocessor\ architecture-Addressing\ modes\ -\ Instruction\ set\ and\ assembler\ directives-Assembly\ language\ programming-Modular\ Programming\ -\ Linking\ and\ Relocation\ -\ Stacks\ -\ Procedures-Macros-Interrupts\ and\ interrupt\ service\ routines-Byte\ and\ String\ Manipulation.$

#### UNIT II 8086 SYSTEM BUS STRUCTURE

9

8086 signals — Basic configurations — System bus ti ming —System design using 8086 — IO programming — Introduction to Multiprogramming — System Bus Structure — Multiprocessor configurations — Coprocessor, Closely coupled and I oosely Coupled configurations — Introduction to advanced processors.

#### UNIT III I/O INTERFACING

9

Memory Interfacing and I/O interfacing - Parallel communication interface - Serial communication interface - D/A and A/D Interface - T imer - Keyboard /display controller - Interrupt controller - DMA controller - Programming and applications Case studies: Traffic Light control, LED display, LCD display, Keyboard display interface and Alarm Controller.

#### UNIT IV MICROCONTROLLER

9

Architecture of 8051 – Special Function Registers(S FRs) - I/O Pins Ports and Circuits - Instruction set - Addressing modes - Assembly language programming.

#### UNIT V INTERFACING MICROCONTROLLER

9

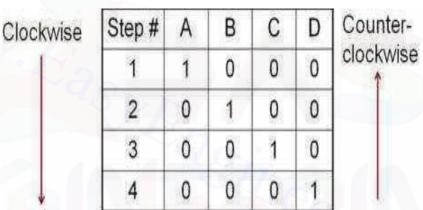

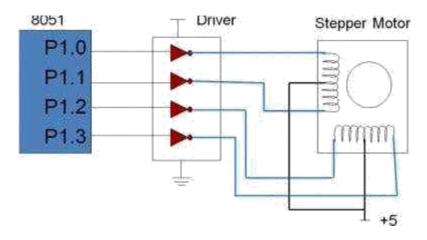

Programming 8051 Timers - Serial Port Programming - Interrupts Programming - LCD & Keyboard Interfacing - ADC, DAC & Sensor Interfacing - External Memory Interface-Stepper Motor and Waveform generation.

#### **TEXT BOOKS:**

1.

- Yu-Cheng Liu, Glenn A.Gibson, "Microcomputer Sys tems: The 8086 / 8088 Family Architecture, Programming and Design", Second Editi on, Prentice Hall of India, 2007.

- 2 Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, "The 8051 microcontroller and Embedded Systems: Using Assembly and C", Second Edition, Pearson Education, 2011

#### **REFERENCE:**

1. Doughlas V.Hall, "Microprocessors and Interfaci ng, Programming and Hardware:,TMH, 2012

#### TABLE OF CONTENTS

| Sl.<br>No |                                   | Торіс                     | Page<br>No. |  |  |  |

|-----------|-----------------------------------|---------------------------|-------------|--|--|--|

| a         | Aim and Objective                 |                           |             |  |  |  |

| b         | Detailed Lesson Plan              | n                         | 2           |  |  |  |

|           | UNIT I                            | THE 8086 MICROPROCESSOR   |             |  |  |  |

| С         | Part A                            |                           | 4           |  |  |  |

| d         | Part B                            |                           | 6           |  |  |  |

| 1.        | Architecture of 808               | 6 Microprocessor          | 6           |  |  |  |

| 2.        | Addressing Modes                  | of 8086                   | 10          |  |  |  |

| 3.        | Instruction Set of 80             | 086                       | 12          |  |  |  |

| 4.        | Assembler Directive               | es and Operators          | 35          |  |  |  |

| 5.        | Modular Programming               |                           |             |  |  |  |

| 6.        | Linking and Relocation            |                           |             |  |  |  |

| 7.        | Stacks                            |                           |             |  |  |  |

| 8.        | Procedures                        |                           |             |  |  |  |

| 9.        | Macros                            |                           | 47          |  |  |  |

| 10.       | Interrupts and Interr             | rupt Routines             | 49          |  |  |  |

|           | UNIT II                           | 8086 SYSTEM BUS STRUCTURE |             |  |  |  |

| e         | Part A                            | ition, Keprise Innov      | 56          |  |  |  |

| f         | Part B                            |                           | 58          |  |  |  |

| 11.       | Pins and Signals of               | 8086                      | 58          |  |  |  |

| 12.       | Minimum Mode 80                   | 86 System and Timings     | 62          |  |  |  |

| 13.       | Maximum Mode 80                   | 986 System and Timings    | 65          |  |  |  |

| 14.       | Multi Processor Configurations 67 |                           |             |  |  |  |

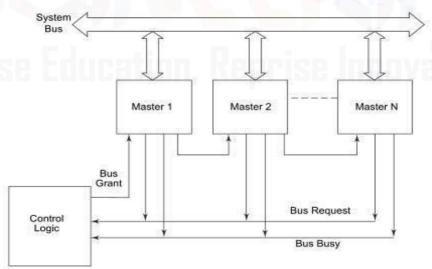

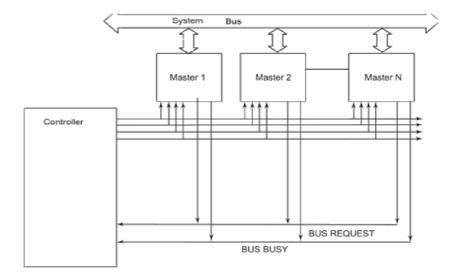

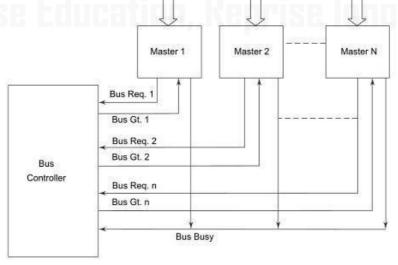

| 15.       | Bus Arbitration                   |                           | 71          |  |  |  |

|           | UN                                | IT III I/O INTERFACING    |             |  |  |  |

| g         | Part A                            |                           | 73          |  |  |  |

| h         | Part B                            |                           | 74          |  |  |  |

| Sl.<br>No | Торіс                                         | Page<br>No. |  |  |  |  |  |  |  |  |

|-----------|-----------------------------------------------|-------------|--|--|--|--|--|--|--|--|

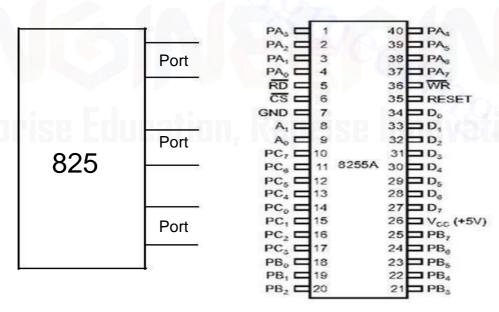

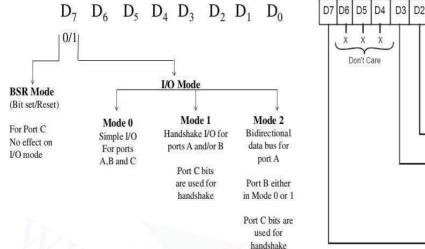

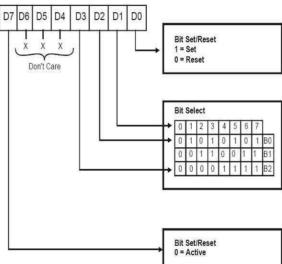

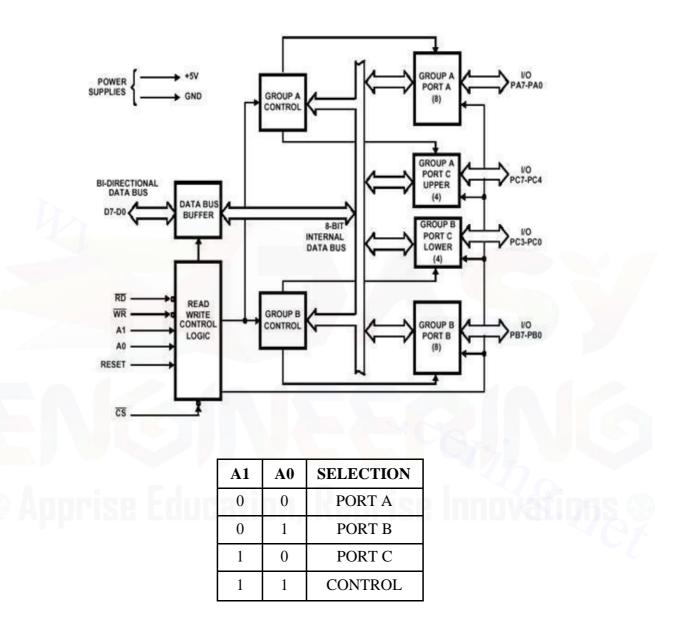

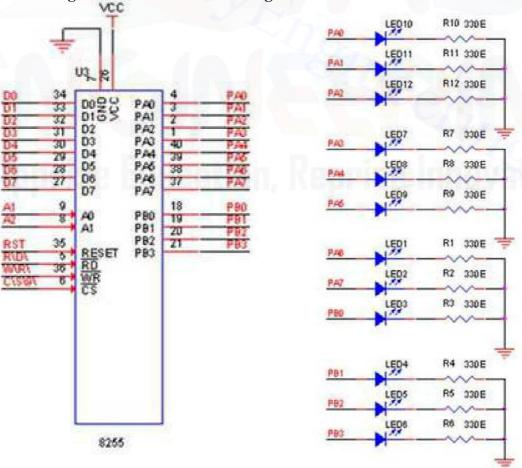

| 16.       | 8255 Programmable Peripheral Interface (Ppi)  | 74          |  |  |  |  |  |  |  |  |

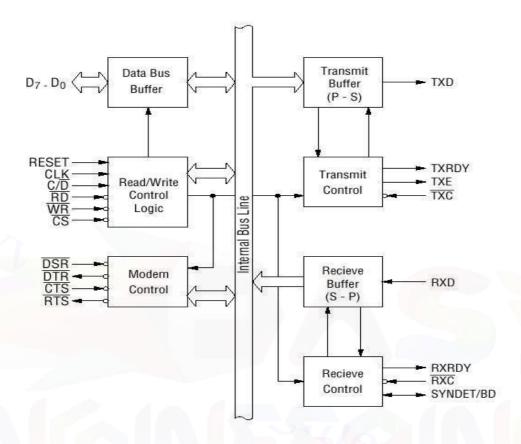

| 17.       | Serial Communication Interface 8251 (Usart)   | 81          |  |  |  |  |  |  |  |  |

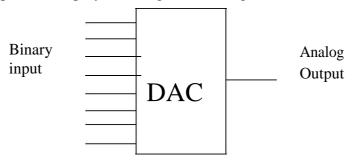

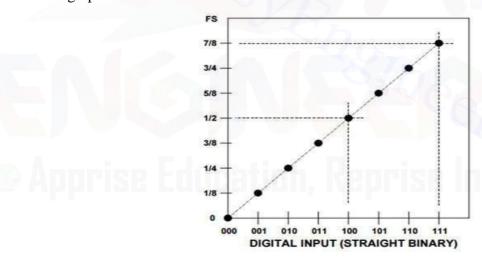

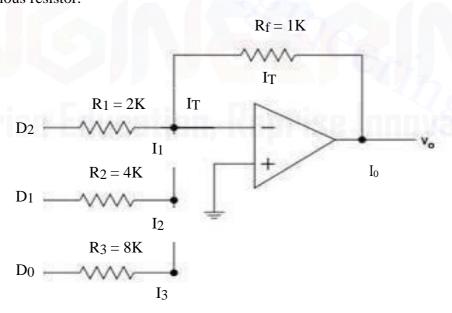

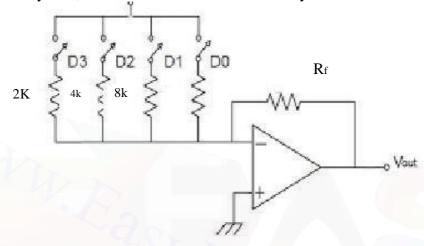

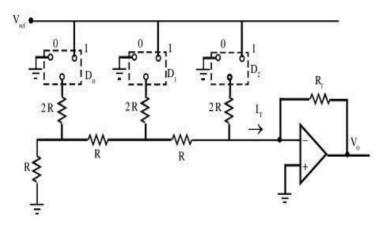

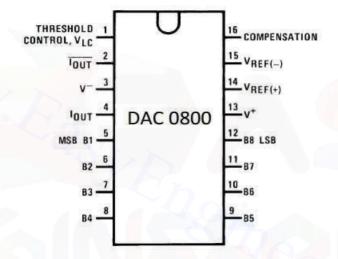

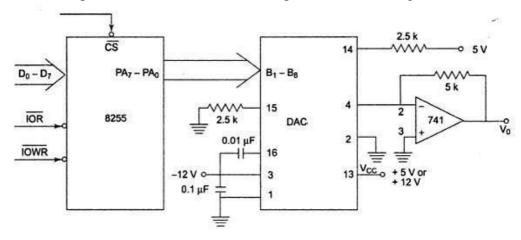

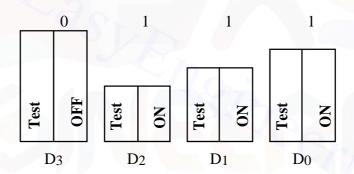

| 18.       | Interfacing Digital To Analog Converters      | 88          |  |  |  |  |  |  |  |  |

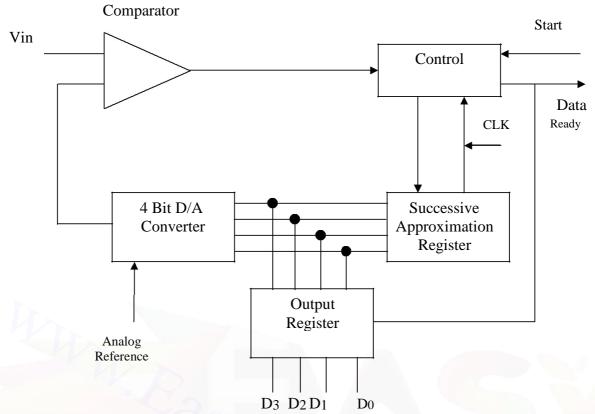

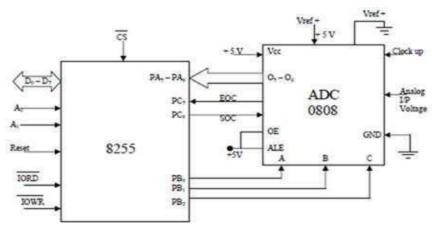

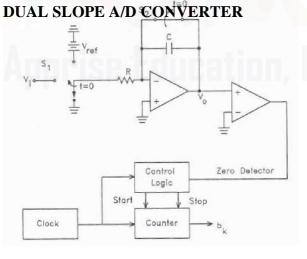

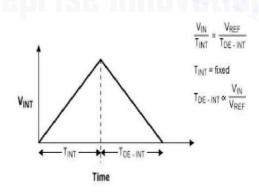

| 19.       | Interfacing Analog To Digital Data Converters | 93          |  |  |  |  |  |  |  |  |

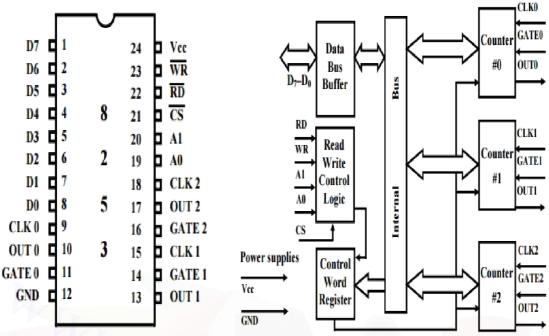

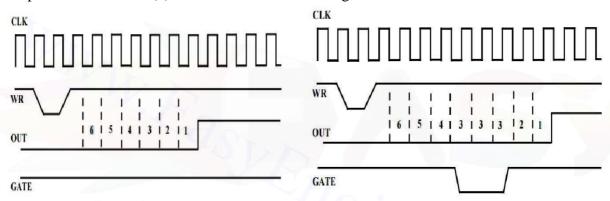

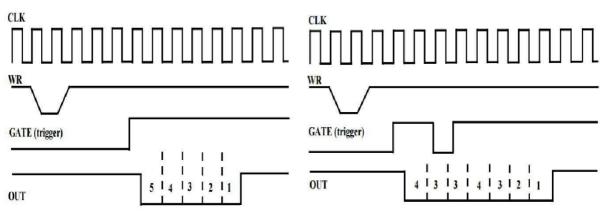

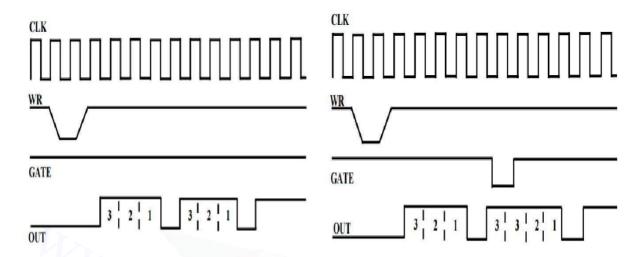

| 20.       | 8253 Programmable Interval Timer              | 97          |  |  |  |  |  |  |  |  |

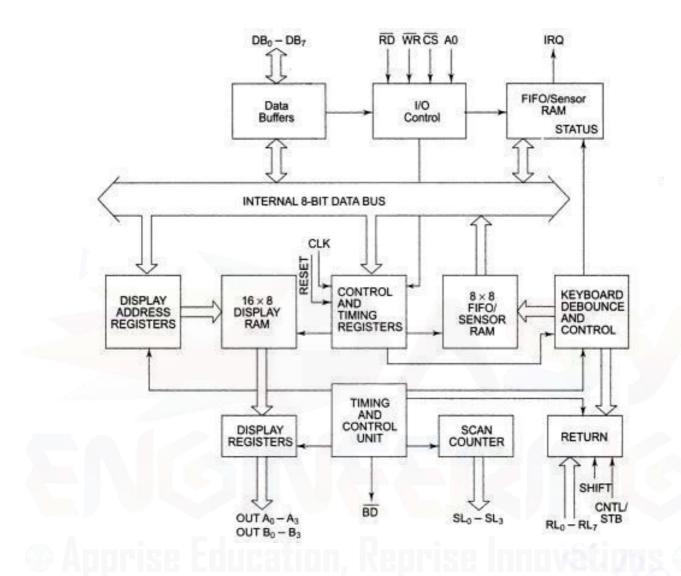

| 21.       | Keyboard and Display Controller (8279)        | 102         |  |  |  |  |  |  |  |  |

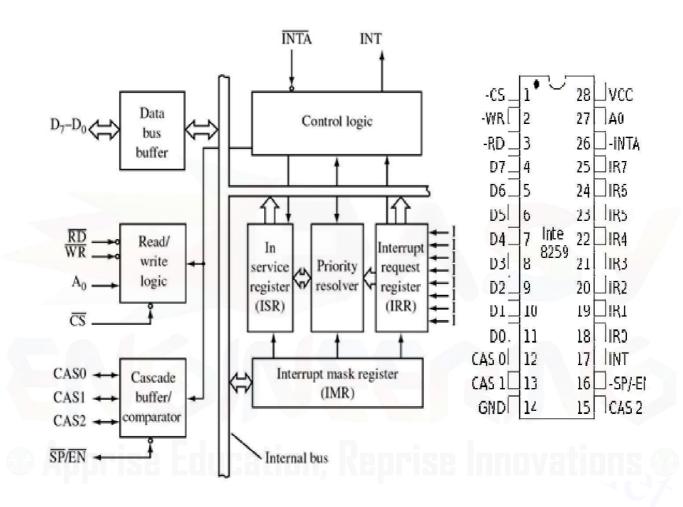

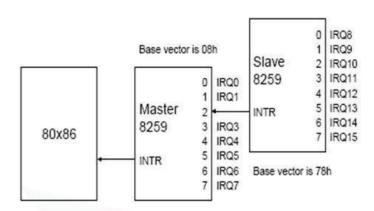

| 22.       | Programmable Interrupt Controller 8259a       | 110         |  |  |  |  |  |  |  |  |

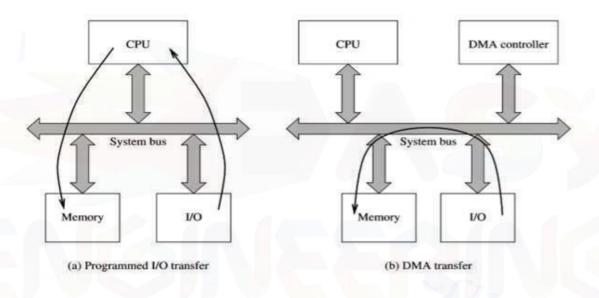

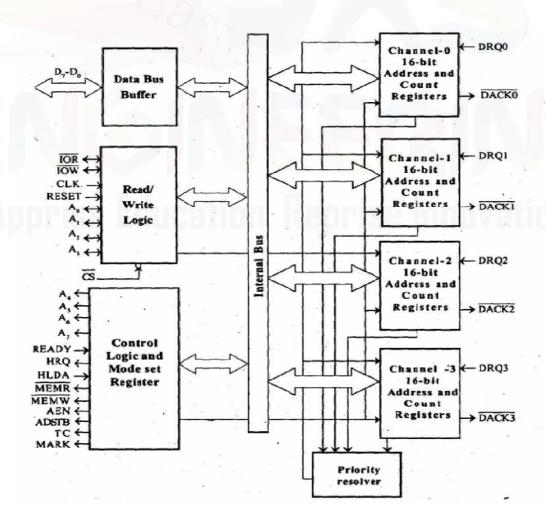

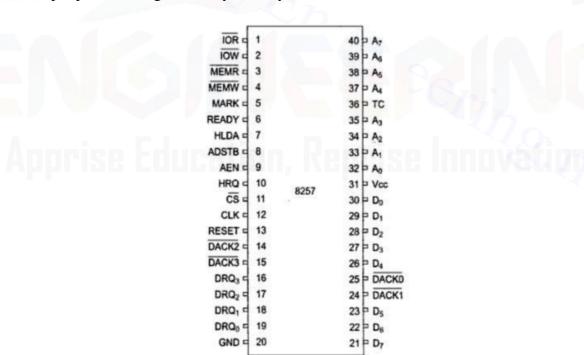

| 23.       | DMA Controller 8257                           | 118         |  |  |  |  |  |  |  |  |

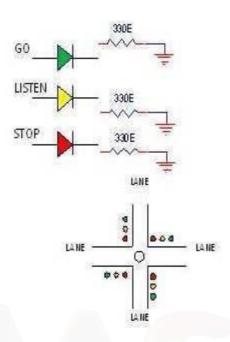

| 24.       | Traffic Light Controller                      | 125         |  |  |  |  |  |  |  |  |

|           | UNIT IV MICROCONTROLLER                       |             |  |  |  |  |  |  |  |  |

| i         | Part A                                        | 128         |  |  |  |  |  |  |  |  |

| j         | Part B                                        | 130         |  |  |  |  |  |  |  |  |

| 25.       | Architecture of 8051                          | 130         |  |  |  |  |  |  |  |  |

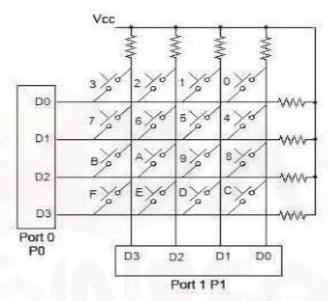

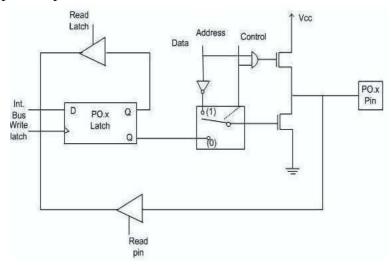

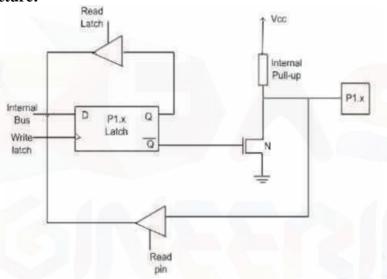

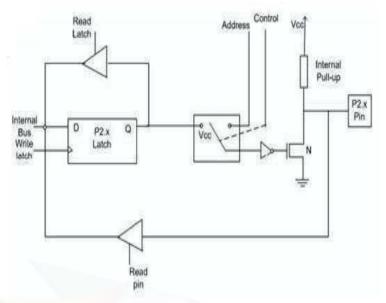

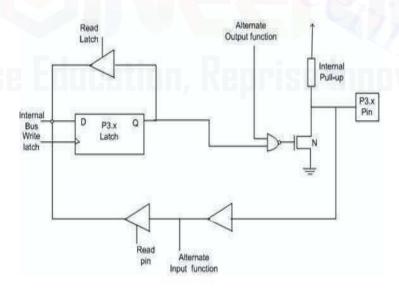

| 26.       | I/O Port Pins, Ports and Circuits             | 137         |  |  |  |  |  |  |  |  |

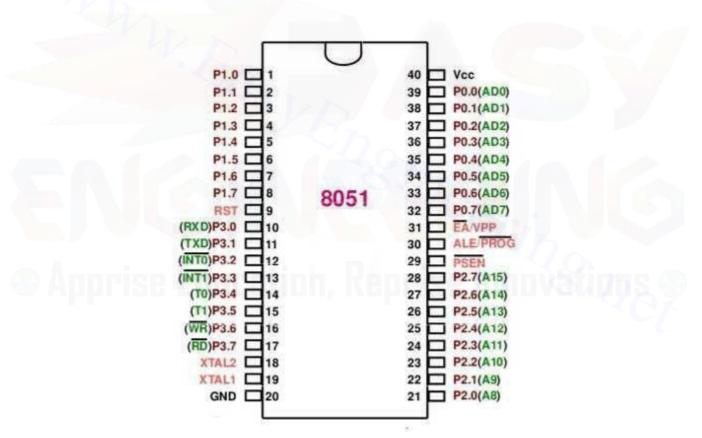

| 27.       | Signals of 8051                               | 140         |  |  |  |  |  |  |  |  |

| 28.       | Instruction Set of 8051                       | 141         |  |  |  |  |  |  |  |  |

| 29.       | Addressing Modes                              | 145         |  |  |  |  |  |  |  |  |

| oor       | UNIT V INTERFACING MICROCONTROLLER            | ation       |  |  |  |  |  |  |  |  |

| k         | Part A                                        | 147         |  |  |  |  |  |  |  |  |

| 1         | Part B                                        | 149         |  |  |  |  |  |  |  |  |

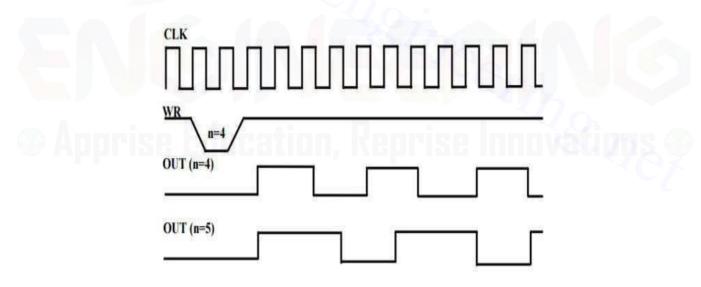

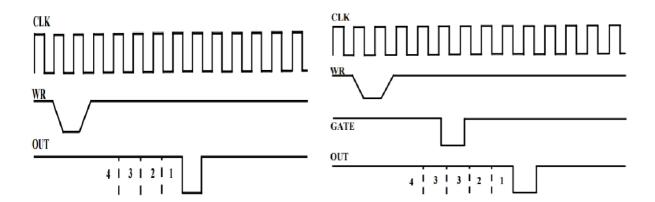

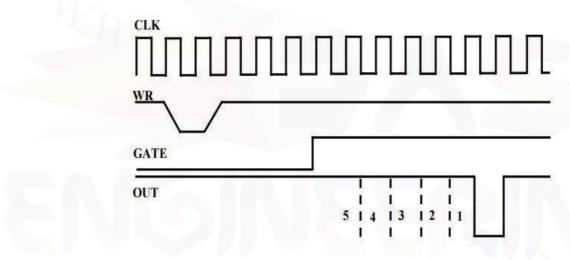

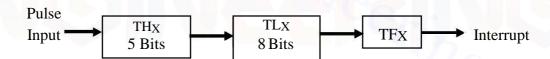

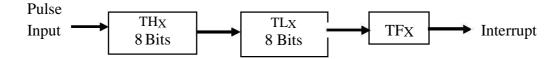

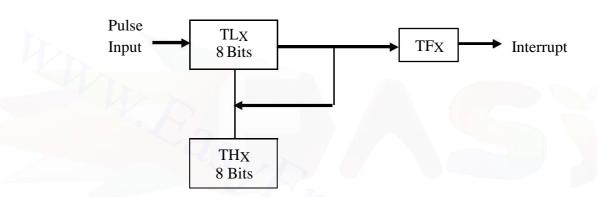

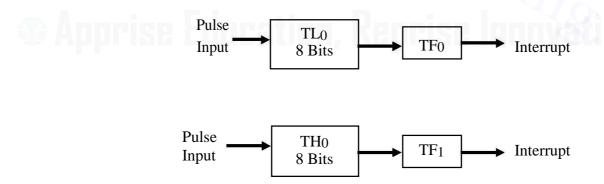

| 30.       | Counters and Timers of 8051                   | 149         |  |  |  |  |  |  |  |  |

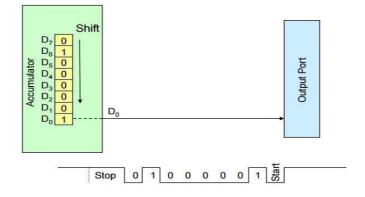

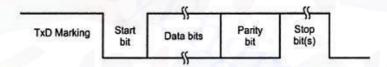

| 31.       | Serial Port Communication                     | 152         |  |  |  |  |  |  |  |  |

| 32.       | Interrupts                                    | 156         |  |  |  |  |  |  |  |  |

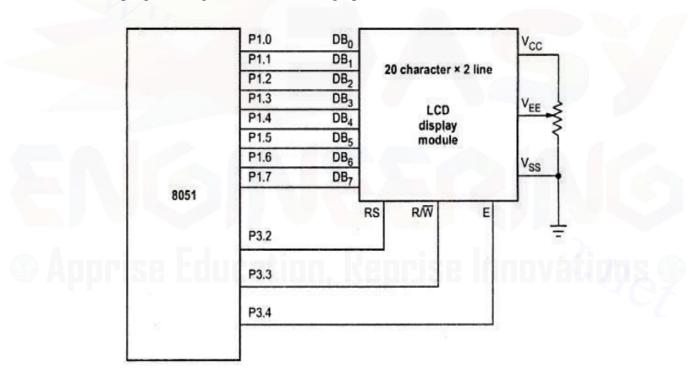

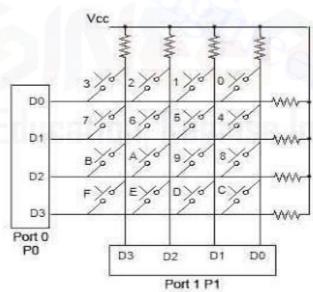

| 33.       | LCD Interfacing and Keyboard Interfacing      | 159         |  |  |  |  |  |  |  |  |

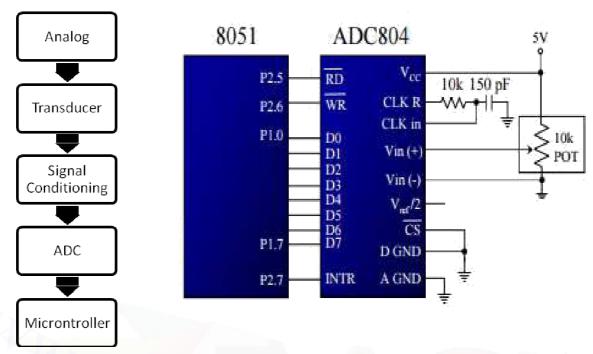

| 34.       | Sensor Interfacing                            | 162         |  |  |  |  |  |  |  |  |

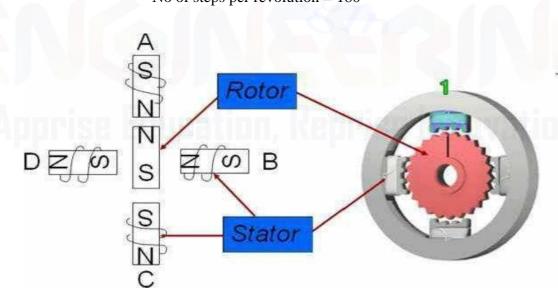

| 35.       | Stepper Motor Interfacing                     | 163         |  |  |  |  |  |  |  |  |

| m         | Industry Connectivity And Latest Developments | 167         |  |  |  |  |  |  |  |  |

#### AIM AND OBJECTIVE OF THE SUBJECT

- To Study the Architecture of 8086 microprocessor.

- To learn the design aspects of I/O and Memory Interfacing circuits.

- To Study about communication and bus interfacing

- To Study the Architecture of 8051 microcontroller.

- To Design and implement programs on 8086 microprocessor.

- To Design I/O circuits.

- To Design Memory Interfacing circuits.

- To Design and implement 8051 microcontroller based systems

#### **DETAILED LESSON PLAN**

#### **Text Book**

- 1. Yu-Cheng Liu, Glenn A.Gibson, "Microcomputer System s: The 8086 / 8088 Family Architecture, Programming and Design", Second Editi on, Prentice Hall of India, 2007.

- 2. Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, "The 8051 Microcontroller and Embedded Systems: Using Assembly and C", Second Edition, Pearson Education, 2011

#### References

1. Doughlas V.Hall, "Microprocessors and Interfacing, Programming and Hardware:, TMH, 2012

| Sl. | Unit | Topic / Portions to be Covered                                       | Hours<br>Required/<br>Planned | Cumulative | Books<br>Referred |

|-----|------|----------------------------------------------------------------------|-------------------------------|------------|-------------------|

| 1   |      | UNIT-I: INTRODUCTI                                                   | ON                            |            |                   |

| 1.  | 1    | Introduction to 8086& Architecture                                   | 1                             | 1          | TB1               |

| 2.  | 1    | Addressing modes, Instruction set                                    | 1                             | 2          | TB1               |

| 3.  | 1    | Assembler directives                                                 | 1                             | 3          | TB1               |

| 4.  | 1    | Assembly language programming                                        | 2                             | 5          | TB1               |

| 5.  | 1    | Modular Programming                                                  | 1                             | 6          | TB1               |

| 6.  | 1    | Linking and Relocation                                               | 1                             | 7          | TB1               |

| 7.  | 1    | Stacks, Procedures, Macros                                           | 1                             | 8          | TB1               |

| 8.  | 1    | Interrupts and interrupt service routines                            | 1                             | 9          | TB1               |

| 9.  | 1    | Byte and String Manipulation                                         | S -1                          | 10         | TB1               |

|     |      | UNIT – II : 8086 SYSTEM BUS S                                        | STRUCTUR                      | E          |                   |

| 10. | 2    | 8086 signals                                                         | 1                             | 11         | TB1               |

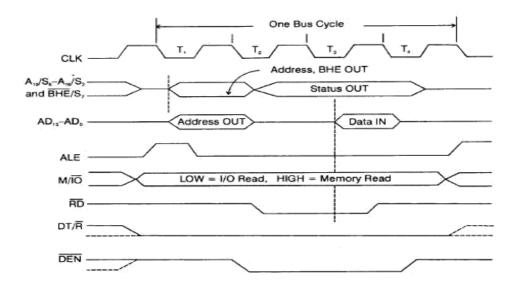

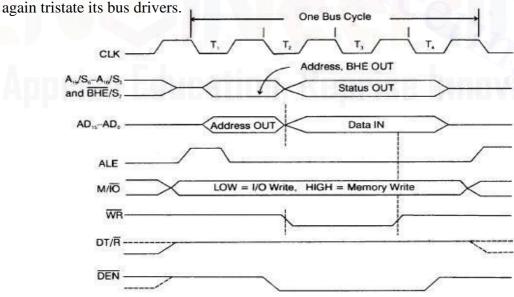

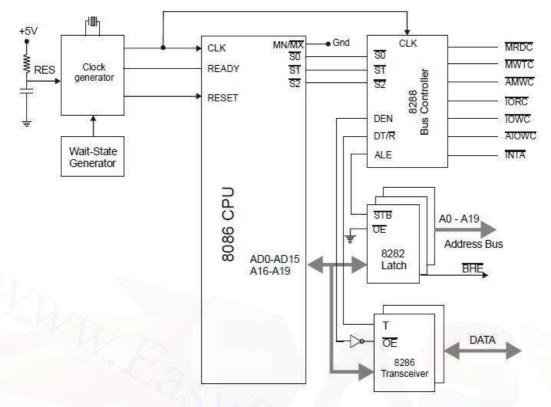

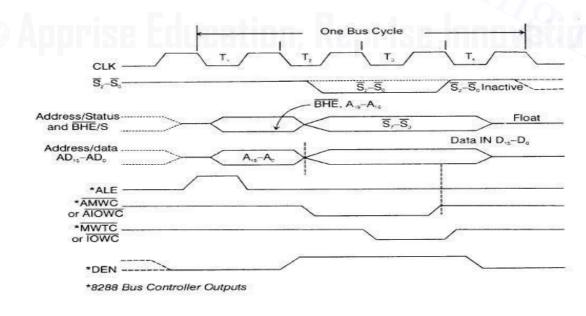

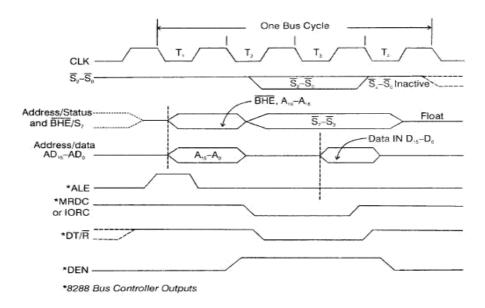

| 11. | 2    | Basic configurations, System bus timing,<br>System design using 8086 | 1                             | 12         | TB1               |

| 12. | 2    | IO programming , Introduction to Multiprogramming                    | 1                             | 13         | TB1               |

| 13. | 2    | System Bus Structure                                                 | 1                             | 14         | TB1               |

| 14. | 2    | Multiprocessor configurations                                        | 1                             | 15         | TB1               |

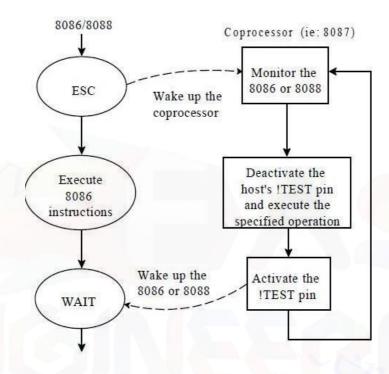

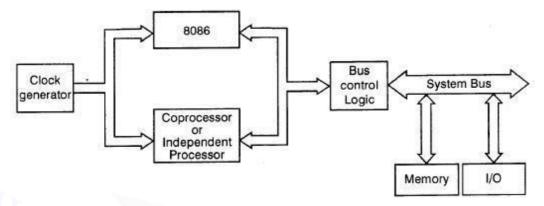

| 15. | 2    | Coprocessor                                                          | 2                             | 17         | TB1               |

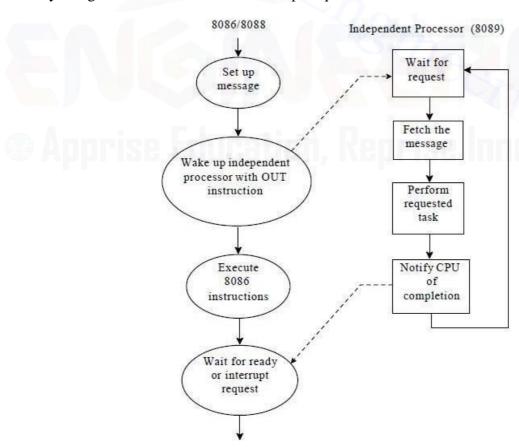

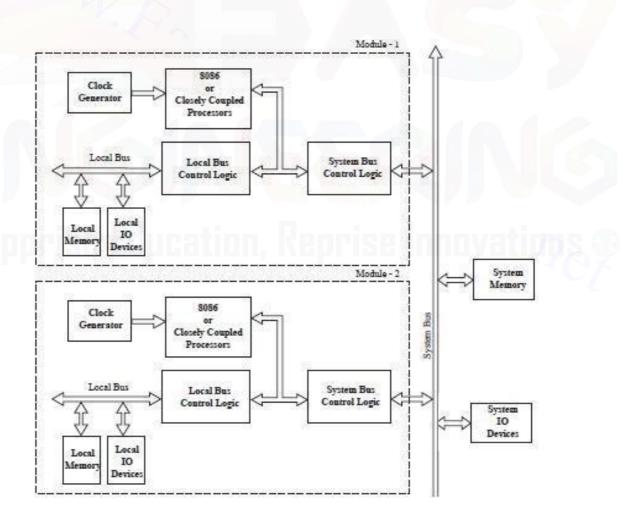

| 16. | 2    | Closely coupled and loosely Coupled configurations                   | 2                             | 19         | TB1               |

| 17. | 2    | Introduction to advanced processors.                                 | 1                             | 20         | TB1               |

| Sl.<br>No | Unit | Topic / Portions to be Covered                                                                                                                       | Hours<br>Required/<br>Planned | Cumulative<br>Hrs | Books<br>Referred |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|-------------------|

|           |      | UNIT- III: I/O INTERFACI                                                                                                                             | ING                           |                   |                   |

| 18.       | 3    | Memory Interfacing and I/O interfacing                                                                                                               | 1                             | 21                | TB1               |

| 19.       | 3    | Parallel communication interface                                                                                                                     | 1                             | 22                | TB1               |

| 20.       | 3    | Serial communication interface                                                                                                                       | 1                             | 23                | TB1               |

| 21.       | 3    | D/A and A/D Interface                                                                                                                                | 1                             | 24                | RB1               |

| 22.       | 3    | Timer                                                                                                                                                | 1                             | 25                | TB1               |

| 23.       | 3    | Keyboard /display controller                                                                                                                         | 1                             | 26                | TB1               |

| 24.       | 3    | Interrupt controller                                                                                                                                 | 1                             | 27                | RB1               |

| 25.       | 3    | DMA controller                                                                                                                                       | 1                             | 28                | TB1               |

| 26.       | 3    | Programming and applications Case studies:<br>Traffic Light control, LED display, LCD<br>display, Keyboard display interface and<br>Alarm Controller | 2                             | 30                | WEB<br>NOTES      |

|           |      | UNIT – IV : MICROCONTRO                                                                                                                              | LLER                          |                   |                   |

| 27.       | 4    | Architecture of 8051                                                                                                                                 | 2                             | 32                | TB2               |

| 28.       | 4    | Special Function Registers(SFRs)                                                                                                                     | 1                             | 33                | TB2               |

| 29.       | 4    | I/O Pins Ports and Circuits                                                                                                                          | 1                             | 34                | TB2               |

| 30.       | 4    | Instruction set                                                                                                                                      | 2                             | 36                | TB2               |

| 31.       | 4    | Addressing modes                                                                                                                                     | 1                             | 37                | TB2               |

| 32.       | 4    | Assembly language programming                                                                                                                        | 2                             | 39                | TB2               |

|           |      | UNIT-V: INTERFACING MICROC                                                                                                                           | ONTROL                        | LER               | Hyn:              |

| 33.       | 5    | Programming 8051 Timers                                                                                                                              | 1                             | 40                | TB2               |

| 34.       | 5    | Serial Port Programming                                                                                                                              | 1                             | 41                | TB2               |

| 35.       | 5    | Interrupts Programming                                                                                                                               | 1                             | 42                | TB2               |

| 36.       | 5    | LCD & Keyboard Interfacing                                                                                                                           | 2                             | 44                | TB2               |

| 37.       | 5    | ADC, DAC & Sensor Interfacing                                                                                                                        | 2                             | 46                | TB2               |

| 38.       | 5    | External Memory Interface                                                                                                                            | 2                             | 48                | TB2               |

| 39.       | 5    | Stepper Motor and Waveform generation.                                                                                                               | 2                             | 50                | TB2               |

#### I THE 8086 MICROPROCESSOR

Introduction to 8086 – Microprocessor architecture – Addressing modes - Instruction set and assembler directives – Assembly language programmin g – Modular Programming - Linking and Relocation - Stacks - Procedures – Macros – Int errupts and interrupt service routines – Byte and String Manipulation.

#### PART A

#### 1. Write about the different types of interrupts supported in 8086. [Apr/May 2015]

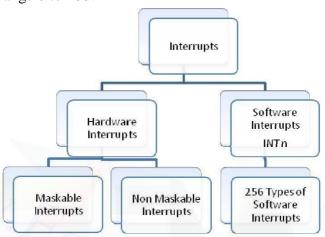

The following are the various types of interrupts:

**Type 0 interrupts**: This interrupt is also known as the divide by zero interrupt. For cases where the quotient becomes particularly large to be placed / adjusted an error might occur.

**Type 1 interrupts**: This is also known as the single step interrupt. This type of interrupt is primarily used for debugging purposes in assembly language.

**Type 2 interrupts**: also known as the non-maskable NMI interrupts. These types of interrupts are used for emergency scenarios such as power failure.

**Type 3 interrupts**: These types of interrupts are also known as breakpoint interrupts. When this interrupt occurs a program would execute up to its break point.

**Type 4 interrupts**: Also known as overflow interrupts is generally existent after an arithmetic Operation was performed.

#### 2. Compare CALL and PUSH instructions CALL PUSH. [Nov/Dec 2011]

| CALL                                                                                                                          | PUSH                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| When CALL is executed the microprocessor automatically stores the 16-bit address of the instruction next to CALL on the stack | instruction PUSH to save the                                              |

| When CALL is executed the stack pointer is decremented by two                                                                 | When PUSH is executed the stack pointer is register is decremented by two |

#### 3. What is assembler? [April/May 2008, Nov/Dec 2011, Apr/May 2011]

The assembler translates the assembly language program text which is given as input to the assembler to their binary equivalents known as object code. The time required to translate the assembly code to object code is called access time. The assembler checks for syntax errors & displays them before giving the object code.

#### 4. What is interrupt service routine?[Nov/Dec 2011]

Interrupt means to break the sequence of operation. While the CPU is executing a program an interrupt breaks the normal sequence of execution of instructions & diverts its execution to some other program. This program to which the control is transferred is called the interrupt service routine.

#### 5. What are Macros? [Nov/Dec 2011]

Macro is a group of instruction. The macro assembler generates the code in the program each time where the macro is called. Macros are defined by MACRO & ENDM directives. Creating macro is similar to creating new opcodes that can be used in the program

INIT MACRO MOV AX, data MOV DS MOV ES, AX ENDM

#### 6. Compare Procedure & Macro [NOV/DEC 2011]

| Procedure                                                        | Macro                                                                    |

|------------------------------------------------------------------|--------------------------------------------------------------------------|

| Accessed by CALL & RET instruction during program execution      | Accessed during assembly with name given to macro when defined           |

| Machine code for instruction is put only once in the memory      | Machine code is generated for instruction each time when macro is called |

| With procedures less memory is required                          | With macro more memory is required                                       |

| Parameters can be passed in registers, memory locations or stack | Parameters passed as part of statement which calls macro                 |

## 7. What is the purpose of segment registers in 8086? [April/May2017, April/May2008, Nov/Dec 2006, 2011]

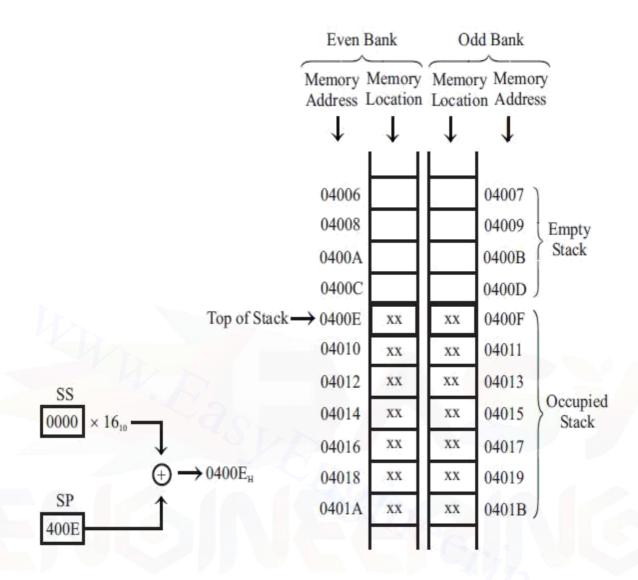

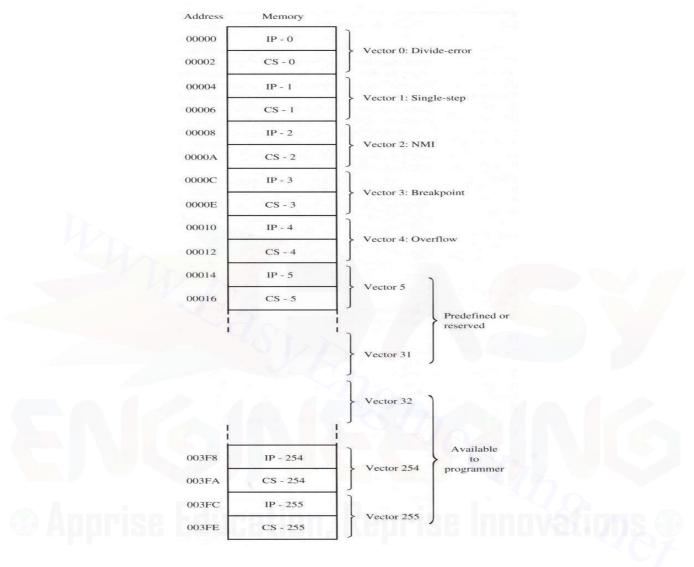

There are 4 segment registers present in 8086. They are Code Segment (CS) register, Data Segment (DS) register, Stack Segment (SS) register, Extra Segment (ES) register. The code segment register gives the address of the current code segment. ie. It will points out where the instructions, to be executed, are stored in the memory. The data segment register points out where the operands are stored in the memory. The stack segment registers points out the address of the current stack, which is used to store the temporary results. If the amount of data used is more, the Extra segment registers points out where the large amount of data is stored in the memory.

#### 8. Define pipelining? [Nov/Dec 2006, Nov/Dec 2011]

In 8086, to speed up the execution of program, the instructions fetching and execution of instructions are overlapped each other. This technique is known as pipelining. In pipelining, when the n<sup>th</sup> instruction is executed, the n+1<sup>th</sup> instruction is fetched and thus the processing speed is increased.

#### 9. Discuss the function of instruction queue in 8086? [Nov/Dec 2006][Apr/May2011]

In 8086, a 6-byte instruction queue is presented at the Bus Interface Unit (BIU). It is used to prefetch and store at the maximum of 6 bytes of instruction code from the memory. Due to this, overlapping instruction fetch with instruction execution increases the processing speed.

#### 10. Draw the Flag register format of 8086? [April/May 2011, nov/Dec 2016]

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5 | 4  | 3 | 2  | 1 | 0  |

|---|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|----|

| Ī | U  | U  | U  | U  | OF | DF | IF | TF | SF | ZF | U | AF | U | PF | U | CF |

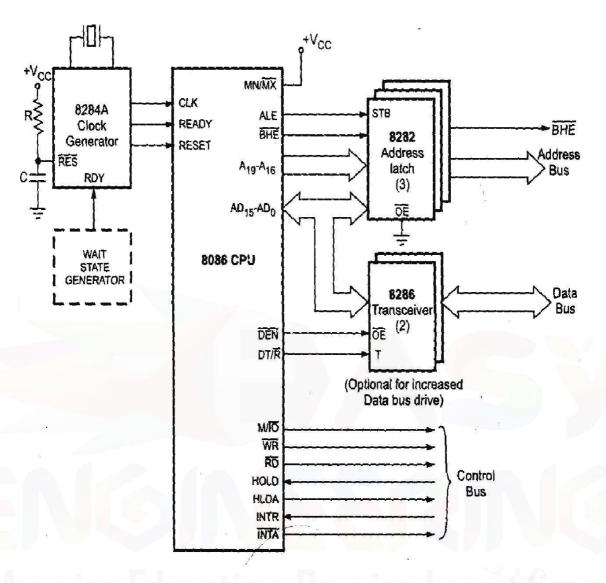

#### 11. What are the two modes of operations present in 8086? [May/June2007]

Minimum Mode (or) Uniprocessor System 2. Maximum Mode (or) Multiprocessor System

#### 12. What are the three classifications of 8086 interrupts? [May/June-2006]

- (1) Predefined Interrupts

- (2) User Defined Hardware Interrupts

- (3) User Defined Software Interrupts.

## 13. What is the processing element inside the microprocessor? What process it does? [Nov/Dec 2014]

The processing element inside the microprocessor is the ALU. It performs all computing operation such as Addition, Subtraction, Multiplication, and Division and Logical operation.

14. Calculate the physical address, when segment address is 1085H and effective address is 4537 H. [Nov/Dec 2015, April 2017]

Effective address= 4537+

Segment address= 1 0 8 5 0

Physical address = 1 4 D 8 7

#### PART B

#### 1. ARCHITECTURE OF 8086 MICROPROCESSOR

Explain briefly about the internal hardware architecture of 8086 microprocessor with a neat diagram. (10)[Apr/May 2015, April/May 2017] Explain the bus interface unit and execution unit of 8086 microprocessor. (8) [Nov/Dec 2014].

Explain The Architecture Of 8086 Microprocessor. (8) [Nov / Dec 2012]

Describe the hardware architecture of 8086 microprocessor with neat diagram. (10) [Nov /Dec 2013]

Explain the internal hardware architecture of 8086 microprocessor with neat diagram.

(12) [April/May 2011]

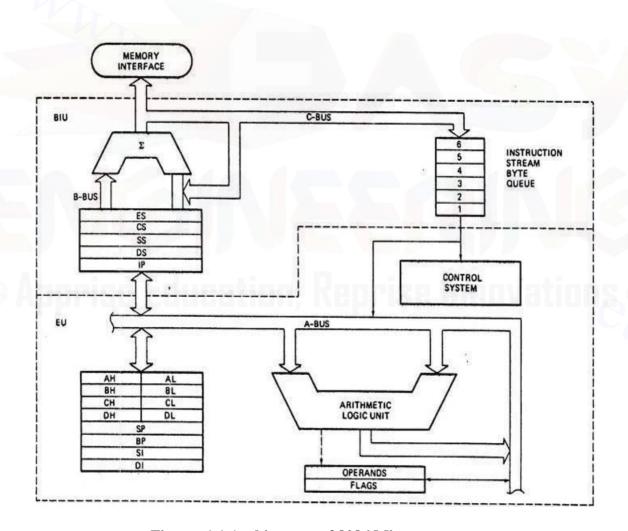

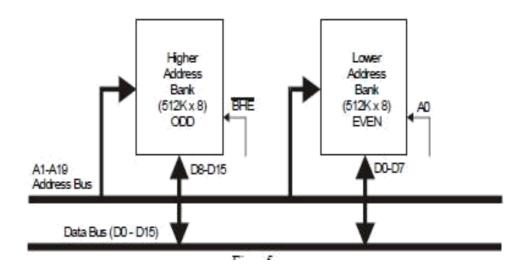

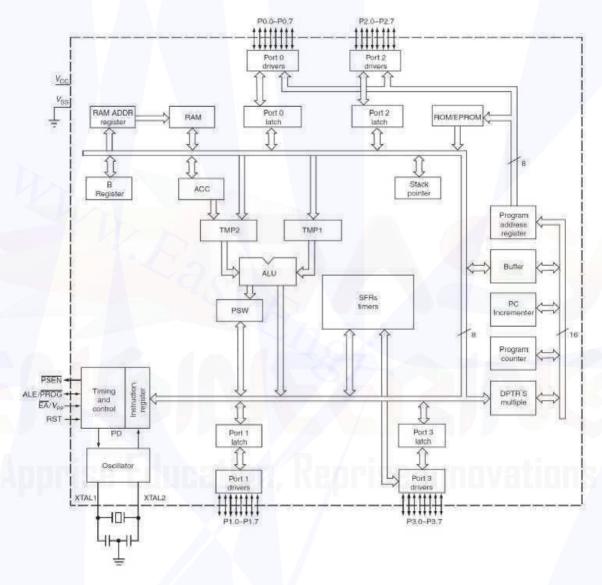

Intel 8086 is a 16 bit processor. It has 16-bit data bus and 20-bit address bus. The lower 16-bit address lines and 16-bit data lines are multiplexed (AD0-AD15). Since 20-bit address lines are available, 8086 can access up to 220 or 1 Giga byte of physical memory. The architecture of the 8086 can be internally divided into two separate functional units as shown in figure 1.1

Bus Interface Unit (BIU) and Execution Unit (EU).

#### **Bus Interface Unit (BIU)**

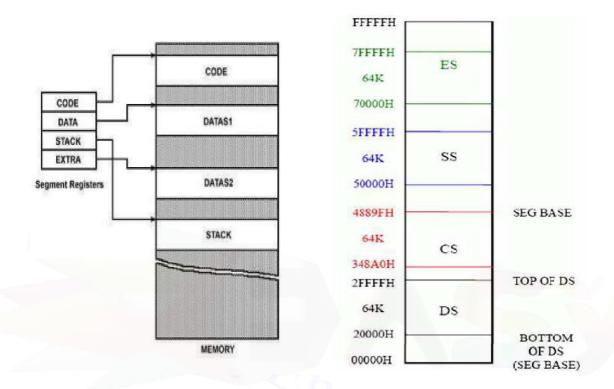

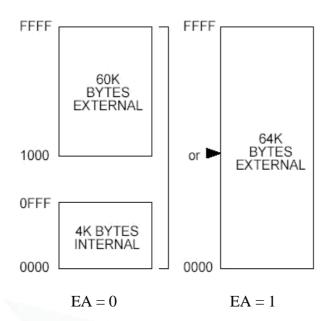

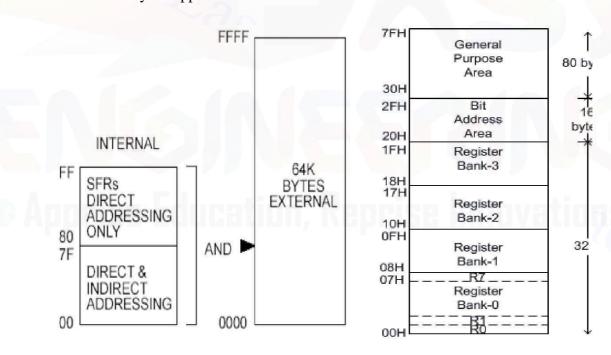

The BIU fetches instructions, reads data from memory and IO ports, writes data to memory and IO ports. The BIU contains segment registers, instruction pointer, instruction queue, address generation unit and bus control unit. The Bus Interface Unit (BIU) generates the 20-bit physical memory address. To speed up the execution, 6-bytes of instruction are fetched in advance and kept in a 6-byte Instruction Queue called pipe-lining. In 8086 microprocessor memory are divided into four parts which is known as the segments as shown in figure 1.2. These segments are data segment, code segment, stack segment and extra segment. Each segments of 64 kilo bytes.

The BIU has four numbers of 16-bit segment registers. They are Code Segment (CS) register, Data Segment (DS) register, Stack Segment (SS) register and Extra Segment (ES) register. The 4 segment registers are used to hold four segment base addresses.

Figure: 1.1 Architecture of 8086 Microprocessor

**Code segment** (CS) is a 16-bit register containing address of 64 KB segment with processor instructions. The programs will be stored in code segment region. The processor uses CS segment for all accesses to instructions referenced by instruction pointer (IP) register.

**Stack segment** (SS) is a 16-bit register containing address of 64KB segment with program stack. Data related with stack operation are stored in this segment region. All data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment.

**Data segment** (DS) is a 16-bit register containing address of 64KB segment with program data. Data referenced by general registers (AX, BX, CX, DX) and index register (SI, DI) is located in the data segment.

**Extra segment** (ES) is a 16-bit register containing address of 64KB segment, usually with program data. The DI register references the ES segment in string manipulation instructions. The address for fetching instruction codes is generated by logically shifting the content of the CS to the left four times and then adding it to the content of the IP (Instruction Pointer). The IP holds the offset address of the program codes.

Code segment Register CS holds the segment address which is 4569 H Instruction pointer IP holds the offset address which is 10A0 H The physical 20-bit address is calculated as follows.

Segment address: 45690 H Offset address: +10A0 H Physical address: 46730 H

The data address is computed by using the content of DS or ES as base address and an offset or effective address specified by the instruction. The stack address is computed by using the content of the SS as base address and the content of the SP (Stack Pointer) as the offset address or effective address.

#### **Execution Unit(EU)**

The EU executes instructions that have already been fetched by the BIU. The BIU and EU function independently. The instruction queue is a FIFO (First-In-First-Out) group of registers. The size of queue is 6 bytes. The BIU fetches instruction code from the memory and stores it in the queue. The EU fetches instruction codes from the queue.

- The EU receives program instruction codes and data from the BIU, executes these instructions, and store the results in the general registers. It receives and outputs all its data through the BIU.

- A decoder in the EU translates instructions fetched from memory into a series of actions which the EU carries out.

The EU has a 16-bit ALU which can add, subtract, AND, OR, XOR, increment, decrement, complement or shift binary numbers. The EU decodes an instruction or executes an instruction.

Figure: 1.2 Memory Organization of 8086 Microprocessor

**Accumulator** register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX.

**Base Register** consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BX register

**Count Register** consists of two 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. Count register can be used as a counter in string manipulation and shift/rotate instructions.

**Data Register** consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. Data register can be used as a port number in I/O operations

The following registers are both general and index registers:

**Stack Pointer** (SP) is a 16-bit register pointing to program stack.

**Base Pointer** (BP) is a 16-bit register pointing to data in stack segment. BP register is usually used for based, based indexed or register indirect addressing.

**Source Index** (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions. **Destination Index** (DI) is a 16-bit register. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions.

**Instruction Pointer** (IP) is a 16-bit register which points to the instruction fetched from memory.

**Flag register** is a 16-bit register containing nine 1-bit flags:

|   |   | _ |   |    |    | -  | -  |    |    | _ |    | _ |    |   | 0  |

|---|---|---|---|----|----|----|----|----|----|---|----|---|----|---|----|

| U | U | U | U | OF | DF | IF | TF | SF | ZF | U | AF | U | PF | U | CF |

U – Undefined SF-Sign Flag

OF-Overflow Flag ZF-Zero Flag

DF-Direction Flag AF-Auxiliary Flag

IF-Interrupt Enable Flag

TF-Single Step Trap Flag

CF-Carry Flag

Overflow Flag (OF) - set if the result is too large positive number, or is too small negative number to fit into destination operand.

Direction Flag (DF) - if set then string manipulation instructions will auto-decrement index registers. If cleared then the index registers will be auto-incremented.

Interrupt-enable Flag (IF) - setting this bit enables maskable interrupts.

Single-step Trap Flag (TF) - if set then single-step interrupt will occur after the next instruction.

Sign Flag (SF) - set if the most significant bit of the result is set. Zero Flag (ZF) - set if the result is zero.

Auxiliary carry Flag (AF) - set if there was a carry from or borrow to bits 0-3 in the AL register during BCD operation.

Parity Flag (PF) - set if parity (the number of "1" bits) in the low-order byte of the result is even.

Carry Flag (CF) - set if there was a carry from or borrow to the most significant bit during last result calculation.

#### 2. ADDRESSING MODES OF 8086

Explain the different addressing modes of 8086 microprocessor with examples. (8) [Nov/Dec 2014].

Explain the different addressing modes of 8086 microprocessor.(16)[Apr/May 2015] Explain the various addressing modes of 8086 processor with suitable examples.(10) [Nov/Dec 2011]

The addressing modes of 8086 are divided into

- Immediate Addressing Mode

- Register Addressing Mode

- Direct Addressing Mode

- Register Indirect Addressing Mode

- String Addressing Mode

- Indexed Addressing Mode

- Base Addressing Mode

- Base Indexed Addressing Mode

- Relative Addressing Mode

- Implied Addressing Mode

#### **Immediate Addressing Mode:**

8 or 16 bit data can be specified as part of the instruction.

Example: MOV CL, 03 H Moves the 8 bit data 03 H into CL

#### **Register Addressing Mode:**

The operand to be accessed is specified as an internal register of 8086.

Example: MOV DX, CX Moves 16 bit content of CX into DX.

#### **Direct Addressing Mode:**

The instruction Opcode is followed by an effective address, this effective address is directly used as the 16 bit offset of the storage location of the operand from the location specified by the current value in the selected segment register.

Example: MOV CX, [5000] If DS = 0050. Then BIU generates the 20 bit physical address 50050 H. The content of 50050 is moved to CL. The content of 50051 is moved to CH.

#### **Register Indirect Addressing Mode:**

The EA is specified in either pointer (BX) register or an index (SI or DI) register. The 20 bit physical address is computed using DS and DI.

Example: MOV BX, [DI]If [DS] = 5000, [DI] = 0020, PA=50020.The

content of 50020 and 50021 is moved to BX Register

#### **String Addressing Mode:**

The string instructions automatically assume SI to point to the first byte or word of the source operand and DI to point to the first byte or word of the destination operand. The contents of SI and DI are automatically incremented (by clearing DF to 0 by CLD instruction) to point to the next byte or word.

Example: MOVSB

If [DF] = 0, [DS] = 2000 H, [SI] = 0500, [ES] = 4000, [DI] = 0300

Source address: 20500, [DS] + [SI]Destination address: <math>[ES] + [DI] = 40300. The data from source address is transferred to the destination address

#### **Indexed Addressing Mode:**

PA = (CS, DS,SS,ES): (SI or DI) + 8 or 16bit displacement

Example: MOV BH, START [SI]

PA: [START] + [SI] + [DS]. The content of this memory is moved into BH.

#### **Base Addressing Mode:**

PA = (CS, DS,SS,ES): (BX or BP) + displacement

Example: MOV AL, START [BX]

EA: [START] + [BX]. The content of this memory is moved into AL

#### **Base Indexed Addressing Mode:**

PA = (CS, DS,SS,ES): (SI or DI) +(BX or BP)+8 or 16 bit displacement

Example: MOV ALPHA [SI] [BX], CL

EA :ALPHA + [SI] + [BX]. The content of CL is moved this memory.

#### **Relative Addressing Mode:**

Example: JNC START

If CY=O, then PC is loaded with current PC contents plus 8 bit signed value of START, otherwise the next instruction is executed.

#### **Implied Addressing Mode:**

Instruction using this mode has no operands.

Example: CLC which clears carry flag to zero.

#### 3. INSTRUCTION SET OF 8086

Give three examples for the following 8086 microprocessor instructions: String Instructions, Process Control Instruction, Program Execution Transfer Instructions and Bit manipulation Instructions. (12 Marks) [April/May 2010]

Explain the data transfer group and logical group of 8086 instructions. [Marks 10] [April/May 2011]

Discuss About The Different Data Transfer Schemes With Examples. (8) [Nov / Dec 2012]

Discuss About The 8086 Instruction Used For Transferring Data Between Registers , Memory , Stacks , And I/O Devices.(8) [Nov / Dec 2012]

Explain the data transfer group and logical group of 8086 instruction with necessary examples. (10) [Nov/Dec 2013]

- a. Data Transfer Instructions

- b. Arithmetic Instructions

- c. Logical Instructions

- d. Shift and Rotate Instructions

- e. Branch Instructions

- f. Loop Instructions

- a. String Manipulating Instructions

- b. Flag Manipulation Instructions.

- c. Stack Related Instructions

- d. Input-Output Instructions

- e. Machine Control Instructions

#### a. DATA TRANSFER INSTRUCTIONS

#### **MOV – MOV Destination, Source**

The MOV instruction copies a word or byte of data from a specified source to a specified destination. The destination can be a register or a memory location. The source can be a register, a memory location or an immediate number.

MOV CX, 037AH

Put immediate number 037AH to CX

| MOV BL, [437AH] | Copy byte in DS at offset 437AH to BL |

|-----------------|---------------------------------------|

| MOV AX, BX      | Copy content of register BX to AX     |

| MOV DL, [BX]    | Copy byte from memory at [BX] to DL   |

#### **XCHG – XCHG Destination, Source**

The XCHG instruction exchanges the content of a register with the content of another register or with the content of memory location(s).

| XCHG AX, DX | Exchange word in AX with word in DX |

|-------------|-------------------------------------|

| XCHG BL, CH | Exchange byte in BL with byte in CH |

#### LEA – LEA Register, Source

This instruction determines the offset of the variable or memory location named as the source and puts this offset in the indicated 16-bit register.

LEA CX, [BX][DI] Load CX with EA = [BX] + [DI]

#### LDS - LDS Register, Memory address of the first wor d

The word from two memory locations is copied into the specified register and the word from the next two memory locations is copied into the DS registers.

LDS BX, [4326]Copy content of memory at displacement 4326H in DS to BL, content of 4327H to BH. Copy content at displacement of 4328H and 4329H in DS to DS register.

#### LES – LES Register, Memory address of the first wor d

The word from the first two memory locations is copied into the specified register, and the word from the next two memory locations is copied into the ES register.

LES BX, [789AH] Copy content of memory at displacement 789AH in DS to BL, content of 789BH to BH, content of memory at displacement 789CH and 789DH in DS is copied to ES register.

#### **b.** ARITHMETIC INSTRUCTIONS

#### ARTHIMETIC INSTRUCTIONS

| ADD<br>ADC | SUB<br>SBB | MUL<br>IMUL | DİV<br>IDIV | INC<br>DEC | DAA<br>DAS | CBW<br>CBW | AAA<br>AAS |

|------------|------------|-------------|-------------|------------|------------|------------|------------|

|            |            |             |             |            |            |            | AAD        |

|            |            |             |             |            |            |            | AAM        |

### **ADD** – **ADD Destination, Source ADC** – **ADC Destination, Source**

These instructions add a number from some *source* to a number in some *destination* and put the result in the specified destination. The ADC also adds the status of the carry flag to the result. The source may be an immediate number, a register, or a memory location.

ADD AL, 74H

ADC CL, BL

ADD DX, [SI]

Add immediate number 74H to content of AL. Result in AL

Add content of BL plus carry status to content of CL

Add word from memory at offset [SI] in DS to content of DX

## **SUB – SUB Destination, Source SBB – SBB Destination, Source**

These instructions subtract the number in some *source* from the number in some *destination* and put the result in the destination. The SBB instruction also subtracts the content of carry flag from the destination. The source may be an immediate number, a register or memory location.

SUB CX, BX CX – BX; Result in CX SUB AX, 3427HSubtract immediate number 3427H from AX

#### **MUL - MUL Source**

This instruction multiplies an *unsigned* byte in some *source* with an *unsigned* byte in AL register or an unsigned word in some *source* with an unsigned word in AX register. When a byte is multiplied by the content of AL, the result (product) is put in AX. When a word is multiplied by the content of AX, the result is put in DX and AX registers.

MUL BL Multiply AL with BL; result in AX

MUL CX Multiply AX with CX; result high word in DX, low word in AX

#### IMUL - IMUL Source

This instruction multiplies a *signed* byte from *source* with a *signed* byte in AL or a *signed* word from some *source* with a *signed* word in AX. When a byte from source is multiplied with content of AL, the signed result (product) will be put in AX. When a word from source is multiplied by AX, the result is put in DX and AX.

IMUL BL Multiply signed byte in AL with signed byte in BL; result in IMUL BX AX. Multiply BX with AX; result in DX and AX

#### DIV - DIV Source

This instruction is used to divide an *unsigned* word by a byte or to divide an *unsigned* double word (32 bits) by a word. When a word is divided by a byte, the word must be in the AX register. The divisor can be in a register or a memory location. After the division, AL will contain the **8-bit quotient**, and AH will contain the **8-bit remainder**.

When a double word is divided by a word, the most significant word of the double word must be in DX, and the least significant word of the double word must be in AX. After the division, AX will contain the **16-bit quotient** and DX will contain the **16-bit remainder**.

DIV BL Divide word in AX by byte in BL; Quotient in AL, remainder in DIV CX AH Divide the word in DX and AX by word in CX; Quotient in AX, and remainder in DX.

#### **IDIV - IDIV Source**

This instruction is used to divide a *signed* word by a *signed* byte, or to divide a *signed* double word by a *signed* word. When dividing a signed word by a signed byte, the word must be in the AX register. The divisor can be in an 8-bit register or a memory location. After the division, AL will contain the signed quotient, and AH will contain the signed remainder.

When dividing a signed double word by a signed word, the most significant word of the dividend (numerator) must be in the DX register, and the least significant word of the dividend must be in the AX register. The divisor can be in any other 16-bit register or memory location. After the division, AX will contain a signed 16-bit quotient, and DX will contain a signed 16-bit remainder.

IDIV BL Signed word in AX/signed byte in BL

IDIV BP Signed double word in DX and AX/signed word in BP

#### **INC – INC Destination**

The INC instruction adds 1 to a specified register or to a memory location..

INC BL Add 1 to content of BL register INC CX Add 1 to content of CX register

#### **DEC – DEC Destination**

This instruction subtracts 1 from the destination word or byte.

DEC CL Subtract 1 from content of CL register DEC BP Subtract 1 from content of BP register

#### DAA (DECIMAL ADJUST AFTER BCD ADDITION)

This instruction is used to convert the result of addition of two packed BCD numbers to a valid BCD number. The result has to be in AL. After an addition if the lower nibble in AL is greater than 9 or AF is set, then the DAA instruction will add 6 to the lower nibble in AL. If the result in the upper nibble of AL is not greater than 9, then the DAA instruction will add 60H to AL.

DAA AL = D7H; upper nibble > 9, add 60H to AL AL = 37 BCD, CF = 1

#### DAS (DECIMAL ADJUST AFTER BCD SUBTRACTION)

This instruction is used after subtracting one packed BCD number from another packed BCD number, to make sure the result is correct packed BCD. The result has to be in AL. If the lower nibble in AL after a subtraction is greater than 9 or the AF was set, then the DAS instruction will subtract 6 from the lower nibble AL. If the result in the upper nibble is now greater than 9 or if the carry flag was set, the DAS instruction will subtract 60 from AL.

Let AL = 49 BCD, and BH = 72 BCD

SUB AL, BH AL = D7H; upper nibble > 9, subtract 60H from DAS AL AL = 77 BCD, CF = 1 (borrow is needed)

#### **CBW (CONVERT SIGNED BYTE TO SIGNED WORD)**

This instruction copies the sign bit of the byte in AL to all the bits in AH. AH is then said to be the sign extension of AL.

Let  $AX = 00000000 \ 10011011 \ (-155 \ decimal)$

**OUTPUT :** AX = 11111111 10011011 (-155 decimal)

#### CWD (CONVERT SIGNED WORD TO SIGNED DOUBLE WORD)

This instruction copies the sign bit of a word in AX to all the bits of the DX register. In other words, it extends the sign of AX into all of DX.

AX = 11110000 11000111 (-3897 decimal)

**OUTPUT**: DX = 11111111 11111111AX = 11110000 11000111 (-3897 decimal)

#### **AAA (ASCII ADJUST FOR ADDITION)**

This instruction is executed after an ADD instruction that adds two ASCII coded operands to give a byte of result in AL. It converts the resulting contents of AL to unpacked decimal digits. After addition AAA instruction examines the lower 4 bits of AL to check whether it contains a valid BCD number in the range 0 to 9. If it is between 0 to 9, AAA instruction sets the higher 4 bits of AL to 0. AH is cleared before addition. If it greater than 9, AAA instruction increments the AL by 06, AH is incremented by 1 and sets the higher 4 bits of AL to 0.

- 1. AL = 07 After AAA AL = 07

- 2. AL = 6A, AH = 00 ie AX 006A after AAA AX = 0100

#### AAS (ASCII ADJUST FOR SUBTRACTION)

Corrects the result in AL register after subtracting two unpacked ASCII operands. If the lower 4 bits are greater than 9 or if AF flag is 0 the AL is decremented by 6 and AH is decremented by 1.

#### AAM (BCD ADJUST AFTER MULTIPLY)

Converts the product available in AL into unpacked BCD format. Before you can multiply two ASCII digits, you must first mask the upper 4 bit of each. This leaves unpacked BCD (one BCD digit per byte) in each byte. After the two unpacked BCD digits are multiplied, the AAM instruction is used to adjust the product to two unpacked BCD digits in AX. AAM works only after the multiplication of two unpacked BCD bytes, and it works only the operand in AL. AAM updates PF, SF and ZF but AF; CF and OF are left undefined.

Let AL = 00000101 (unpacked BCD 5), and BH = 00001001 (unpacked BCD 9)

MUL BH AL x BH:  $AX = 00000000 \ 00101101 = 002DH$

AAM  $AX = 00000100\ 00000101 = 0405H \text{ (unpacked BCD for 45)}$

#### AAD (BCD-TO-BINARY CONVERT BEFORE DIVISION)

AAD converts two unpacked BCD digits in AH and AL to the equivalent binary number in AL. This adjustment must be made before dividing the two unpacked BCD digits in AX by an unpacked BCD byte. After the BCD division, AL will contain the unpacked BCD quotient and AH will contain the unpacked BCD remainder. AAD updates PF, SF and ZF; AF, CF and OF are left undefined.

Let AX = 0607 (unpacked BCD for 67 decimal), and CH = 09H

AAD AX = 0043 (43H = 67 decimal)DIV CH AL = 07; AH = 04; Flags undefined after DIV

If an attempt is made to divide by 0, the 8086 will generate a type 0 interrupt.

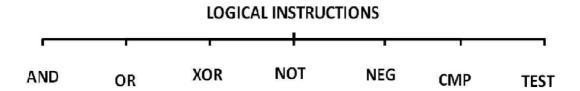

#### c. LOGICAL INSTRUCTIONS

#### **AND – AND Destination, Source**

This instruction ANDs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination.

AND BH, CL AND byte in CL with byte in BH; Result in BH AND BX, 00FFH Masks upper byte, leaves lower byte unchanged.

#### **OR – OR Destination, Source**

This instruction ORs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination.

OR AH, CL CL ORed with AH, result in AH, CL not changed OR BL. 80HBL ORed with immediate number 80H; sets MSB of BL to 1

#### **XOR – XOR Destination, Source**

This instruction Exclusive-ORs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination.

| XOR CL, BH | Byte in BH exclusive-ORed with byte in CL .Result in CL. |

|------------|----------------------------------------------------------|

| XOR BP, DI | Word in DI exclusive-ORed with word in BP. Result in BP. |

#### **NOT – NOT Destination**

The NOT instruction inverts each bit (forms the 1's complement) of a byte or word in the specified destination.

NOT BX Complement content or BX register

#### **NEG – NEG Destination**

This instruction replaces the number in a destination with its 2's complement. It gives the same result as the *invert each bit and add one* algorithm.

NEG AL Replace number in AL with its 2's complement

#### **CMP – CMP Destination, Source**

This instruction compares a byte / word in the specified source with a byte / word in the specified destination. The comparison is actually done by **subtracting** the source byte or

word from the destination byte or word. The source and the destination are not changed, but the flags are set to indicate the results of the comparison.

|             | CF | $\mathbf{Z}\mathbf{F}$ | SF |                                              |

|-------------|----|------------------------|----|----------------------------------------------|

| CX = BX     | 0  | 1                      | 0  | Result of subtraction is 0                   |

| CX > BX     | 0  | 0                      | 0  | No borrow required, so $CF = 0$              |

| CX < BX     | 1  | 0                      | 1  | Subtraction requires borrow, so $CF = 1$     |

| CMP AL, 01H |    |                        |    | Compare immediate number 01H with byte in AL |

| CMP BH, CL  |    |                        |    | Compare byte in CL with byte in BH           |

#### **TEST – TEST Destination, Source**

This instruction ANDs the byte / word in the specified source with the byte / word in the specified destination. **Flags are updated, but neither operand is changed**. The test instruction is often used to set flags before a Conditional jump instruction.

TEST AL, BH

AND BH with AL. No result stored; Update PF, SF, ZF.

#### d. ROTATE AND SHIFT INSTRUCTIONS

# ROTATE AND SHIFT INSTRUCTIONS RCL RCR ROL ROR SAL SAR SHR

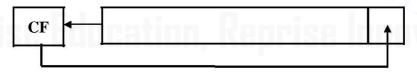

#### **RCL – RCL Destination, Count**

This instruction rotates all the bits in a specified word or byte some number of bit positions to the left. The operation is circular because the MSB of the operand is rotated into the carry flag and the bit in the carry flag is rotated around into LSB of the operand.

To rotate the operand by one bit position, specify this by putting a 1 in the count position of the instruction. To rotate by more than one bit position, load the desired number into the CL register and put "CL" in the count position of the instruction.

RCL DX, 1Word in DX 1 bit left

MOV CL, 4Load the number of bit positions to rotate into CL

RCL DX, CL Rotate DX register content 4 times left

#### **RCR – RCR Destination, Count**

This instruction rotates all the bits in a specified word or byte some number of bit positions to the right. The operation is circular because the LSB of the operand is rotated into the carry flag and the bit in the carry flag is rotated around into MSB of the operand.

If you want to rotate the operand by one bit position, you can specify this by putting a 1 in the count position of the instruction. To rotate more than one bit position, load the desired number into the CL register and put "CL" in the count position of the instruction.

RCR BX, 1 Word in BX right 1 bit

MOV CL, 4 Load CL for rotating 4 bit position RCRBX, CL Rotate BX register content 4 times right

#### **ROL – ROL Destination, Count**

This instruction rotates all the bits in a specified word or byte to the left some number of bit positions. The data bit rotated out of MSB is circled back into the LSB. It is also copied into CF.

If you to want rotate the operand by one bit position, you can specify this by putting 1 in the count position in the instruction. To rotate more than one bit position, load the desired number into the CL register and put "CL" in the count position of the instruction.

ROL AX, 1 Rotate the word in AX 1 bit position left MOV CL, 04HLoad number of bits to rotate in CL

ROL BL, CL Rotate BL register content 4 times left

#### **ROR – ROR Destination, Count**

This instruction rotates all the bits in a specified word or byte some number of bit positions to right. The operation is desired as a rotate rather than shift, because the bit moved out of the LSB is rotated around into the MSB. The data bit moved out of the LSB is also copied into CF.

To rotate the operand by one bit position, specify this by putting 1 in the count position in the instruction. To rotate by more than one bit position, load the desired number into the CL register and put "CL" in the count position of the instruction.

ROR BL, 1 Rotate all bits in BL right 1 bit position

#### **SAL – SAL Destination, Count**

#### SHL – SHL Destination, Count

This instruction shifts each bit in the specified destination some number of bit positions to the left. As a bit is shifted out of the LSB operation, a 0 is put in the LSB position. The MSB will be shifted into CF.

To shift the operand by one bit position, specify this by putting a 1 in the count position of the instruction. For shifts of more than 1 bit position, load the desired number of shifts into the CL register, and put "CL" in the count position of the instruction.

SAL BX, 1 Shift word in BX 1 bit position left, 0 in LSB MOV CL, 02H Load desired number of shifts in CL SAL BX, CL Shift word in BX left CL bit positions, 0 in LSBs

#### SAR – SAR Destination, Count

This instruction shifts each bit in the specified destination some number of bit positions to the right. As a bit is shifted out of the MSB position, a copy of the old MSB is put in the MSB position. In other words, the sign bit is copied into the MSB. The LSB will be shifted into CF

To shift the operand by one bit position, specify this by putting a 1 in the count position of the instruction. For shifts of more than 1 bit position, load the desired number of shifts into the CL register, and put "CL" in the count position of the instruction.

SAR DX, 1Shift word in DX one bit position right, new MSB = old MSB

#### **SHR – SHR Destination, Count**

This instruction shifts each bit in the specified destination some number of bit positions to the right. As a bit is shifted out of the MSB position, a 0 is put in its place. The bit shifted out of the LSB position goes to CF.

To shift the operand by one bit position, specify this by putting a 1 in the count position of the instruction. For shifts of more than 1 bit position, load the desired number of shifts into the CL register, and put "CL" in the count position of the instruction.

SHR BP, 1 Shift word in BP one bit position right, 0 in MOV CL, 03H MSB Load desired number of shifts into CL SHR BP, CL Shift BP register content 3 bits right; 0's in 3 MSBs

#### e. BRANCH INSTRUCTIONS

• JA/JNBE • JNE / JNZ

• JB/JC/JNAE • JS

• JBE/JNA • JNS

• JG/JNLE • JP / JPE

• JGE/JNL • JNP/JPO

• JL/JNGE • JO

• JLE/JNG • JNO

• JE/JZ • JCXZ

#### JMP (UNCONDITIONAL JUMP TO SPECIFIED DESTINATION)

This instruction will fetch the next instruction from the location specified in the instruction rather than from the next location after the JMP instruction. Two types of Jump instruction. Far Jump and Near Jump

If the destination is in the same code segment as the JMP instruction, then only the instruction pointer will be changed to get the destination location. This is referred to as a near jump.

If the destination for the jump instruction is in a segment with a name different from that of the segment containing the JMP instruction, then both the instruction pointer and the code segment register content will be changed to get the destination location. This referred to as a *far jump*. The JMP instruction does not affect any flag.

#### JMP CONTINUE

This instruction fetches the next instruction from address at label CONTINUE.

#### JA / JNBE JUMP IF ABOVE / JUMP IF NOT BELOW OR EQUAL)

If, after a compare or some other instructions which affect flags, the zero flag and the carry flag both are 0, this instruction will cause execution to jump to a label given in the instruction. If CF and ZF are not both 0, the instruction will have no effect on program execution.

JA NEXT Jump to label NEXT if AX above 4371H

CMP AX, 4371H Compare (AX - 4371H)

Jump to label NEXT if AX not below or equal to 4371H JNBE NEXT

#### JAE / JNB / JNC

#### (JUMP IF ABOVE OR EQUAL / JUMP IF NOT BELOW / JUMP IF NO CARRY)

If, after a compare or some other instructions which affect flags, the carry flag is 0, this instruction will cause execution to jump to a label given in the instruction. If CF is 1, the instruction will have no effect on program execution.

CMP AX, 4371H Compare (AX - 4371H)JAE NEXT

Jump to label NEXT if AX above 4371H

CMP AX, 4371H Compare (AX – 4371H)

JNB NEXT Jump to label NEXT if AX not below 4371H

#### JB / JC / JNAE

#### (JUMP IF BELOW / JUMP IF CARRY / JUMP IF NOT ABOVE OR EQUAL)

If, after a compare or some other instructions which affect flags, the carry flag is a 1, this instruction will cause execution to jump to a label given in the instruction. If CF is 0, the instruction will have no effect on program execution.

CMP AX, 4371H Compare (AX – 4371H)

JB NEXT Jump to label NEXT if AX below 4371H

ADD BX, CX Add two words

JC NEXT Jump to label NEXT if CF = 1

#### JBE / JNA (JUMP IF BELOW OR EQUAL / JUMP IF NOT ABOVE)

If, after a compare or some other instructions which affect flags, either the zero flag or the carry flag is 1, this instruction will cause execution to jump to a label given in the instruction. If CF and ZF are both 0, the instruction will have no effect on program execution.

CMP AX, 4371H Compare (AX – 4371H)

JBE NEXT Jump to label NEXT if AX is below or equal to 4371H

CMP AX, 4371H Compare (AX – 4371H)

JNA NEXT Jump to label NEXT if AX not above 4371H

#### JG / JNLE (JUMP IF GREATER / JUMP IF NOT LESS THAN OR EQUAL)

This instruction is usually used after a Compare instruction. The instruction will cause a jump to the label given in the instruction, if the zero flag is 0 and the carry flag is the same as the overflow flag.

CMP BL, 39HCompare by subtracting 39H from BL

CMP BL, 39HCompare by subtracting 39H from BL

JNLE NEXT Jump to label NEXT if BL is not less than or equal to 39H

#### JGE / JNL (JUMP IF GREATER THAN OR EQUAL / JUMP IF NOT LESS THAN)

This instruction is usually used after a Compare instruction. The instruction will cause a jump to the label given in the instruction, if the sign flag is equal to the overflow flag.

CMP BL, 39H Compare by subtracting 39H from BL

Jump to label NEXT if BL more positive than

JGE NEXT or equal to 39H

CMP BL, 39H Compare by subtracting 39H from BL

JNL NEXT Jump to label NEXT if BL not less than 39H

#### JL / JNGE (JUMP IF LESS THAN / JUMP IF NOT GREATER THAN OR EQUAL)

This instruction is usually used after a Compare instruction. The instruction will cause a jump to the label given in the instruction if the sign flag is not equal to the overflow flag.

CMP BL, 39HCompare by subtracting 39H from BL

JL AGAIN Jump to label AGAIN if BL more negative than 39H

CMP BL, 39HCompare by subtracting 39H from BL

JNGE AGAINJump to label AGAIN if BL not more positive than or equal to 39H

#### JLE / JNG (JUMP IF LESS THAN OR EQUAL / JUMP IF NOT GREATER)

This instruction is usually used after a Compare instruction. The instruction will cause a jump to the label given in the instruction if the zero flag is set, or if the sign flag not equal to the overflow flag.

CMP BL, 39HCompare by subtracting 39H from BL

JLE NEXT Jump to label NEXT if BL more negative than or equal to 39H

CMP BL, 39HCompare by subtracting 39H from BL

JNG NEXT Jump to label NEXT if BL not more positive than 39H

#### JE / JZ (JUMP IF EQUAL / JUMP IF ZERO)

This instruction is usually used after a Compare instruction. If the zero flag is set, then this instruction will cause a jump to the label given in the instruction.

CMP BX, DX

JE DONE

IN AL, 30H

Compare (BX-DX)

Jump to DONE if BX = DX

Read data from port 8FH

SUB AL, 30H Subtract the minimum value.

JZ START Jump to label START if the result of subtraction is 0

#### JNE / JNZ (JUMP NOT EQUAL / JUMP IF NOT ZERO)

This instruction is usually used after a Compare instruction. If the zero flag is 0, then this instruction will cause a jump to the label given in the instruction.

IN AL, 0F8H Read data value from port CMP AL, 72 Compare (AL –72)

JNE NEXT Jump to label NEXT if  $AL \neq 72$

#### JS (JUMP IF SIGNED / JUMP IF NEGATIVE)

This instruction will cause a jump to the specified destination address if the sign flag is set. Since a 1 in the sign flag indicates a negative signed number, you can think of this instruction as saying "jump if negative".

ADD BL, DH Add signed byte in DH to signed byte in DL

JS NEXT Jump to label NEXT if result of addition is negative number

#### JNS (JUMP IF NOT SIGNED / JUMP IF POSITIVE)

This instruction will cause a jump to the specified destination address if the sign flag is 0. Since a 0 in the sign flag indicate a positive signed number, you can think to this instruction as saying "jump if positive".

DEC AL Decrement AL

JNS NEXT Jump to label NEXT if AL has not decremented to FFH

#### JP / JPE (JUMP IF PARITY / JUMP IF PARITY EVEN)

If the number of 1's left in the lower 8 bits of a data word after an instruction which affects the parity flag is even, then the parity flag will be set. If the parity flag is set, the JP / JPE instruction will cause a jump to the specified destination address.

IN AL, 0F8H Read ASCII character from Port F8H

OR AL, AL Set flags

JPE ERROR Odd parity expected, send error message if parity found even

#### JNP / JPO (JUMP IF NO PARITY / JUMP IF PARITY ODD)

If the number of 1's left in the lower 8 bits of a data word after an instruction which affects the parity flag is odd, then the parity flag is 0. The JNP / JPO instruction will cause a jump to the specified destination address, if the parity flag is 0.

IN AL, 0F8H Read ASCII character from Port F8H

OR AL, AL Set flags

JPO ERROR Even parity expected, send error message if parity found odd

#### **JO (JUMP IF OVERFLOW)**

The overflow flag will be set if the magnitude of the result produced by some signed arithmetic operation is too large to fit in the destination register or memory location. The JO instruction will cause a jump to the destination given in the instruction, if the overflow flag is set.

ADD AL, BL Add signed bytes in AL and BL

JO ERROR Jump to label ERROR if overflow from add

#### JNO (JUMP IF NO OVERFLOW)

The overflow flag will be set if some signed arithmetic operation is too large to fit in the destination register or memory location. The JNO instruction will cause a jump to the destination given in the instruction, if the overflow flag is not set.

ADD AL, BL Add signed byte in AL and BL JNO DONE Process DONE if no overflow

#### JCXZ (JUMP IF THE CX REGISTER IS ZERO)

This instruction will cause a jump to the label to a given in the instruction, if the CX register contains all 0's. The instruction does not look at the zero flag when it decides whether to jump or not.

JCXZ SKIP SUB [BX], 07H

SKIP: ADD C

If CX = 0, skip the process Subtract 7 from data value Next instruction

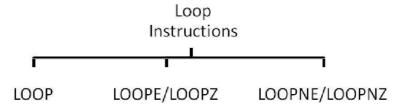

#### f. LOOP INSTRUCTIONS

**LOOP (JUMP TO SPECIFIED LABEL IF CX \neq 0 AFTER AUTO DECREMENT)** This instruction is used to repeat a series of instructions some number of times. The number of times the instruction sequence is to be repeated is loaded into CX. Each time the LOOP

instruction executes, CX is automatically decremented by 1.

MOV BX, [4000] Point BX at first element in array

MOV CX, 40 Load CX with number of elements in array

NEXT: MOV AL, [BX] Get element from array

INC AL Increment the content of AL

MOV [BX], AL Put result back in array

INC BX Increment BX to point to next location LOOP NEXT Repeat until all elements adjusted

#### LOOPE / LOOPZ (LOOP WHILE $CX \neq 0$ AND ZF = 1)

This instruction is used to repeat a group of instructions some number of times, or until the zero flag becomes 0. The number of times the instruction sequence is to be repeated is loaded into CX. Each time the LOOP instruction executes, CX is automatically decremented by 1. If  $CX \neq 0$  and ZF = 1, execution will jump to a destination specified by a label in the instruction. If CX = 0, execution simply go on the next instruction after LOOPE / LOOPZ.

MOV BX, [4000] Point BX to address before start of array

DEC BX Decrement BX

MOV CX, 100 Put number of array elements in CX

NEXT: INC BX

Point to next element in array

CMP [BX], OFFH Compare array element with FFH

LOOPE NEXT

#### **LOOPNE / LOOPNZ (LOOP WHILE CX \neq 0 AND ZF = 0)**

This instruction is used to repeat a group of instructions some number of times, or until the zero flag becomes a 1. The number of times the instruction sequence is to be repeated is loaded into the count register CX. Each time the LOOPNE / LOOPNZ instruction executes, CX is automatically decremented by 1. If  $CX \neq 0$  and ZF = 0, execution will jump to a destination specified by a label in the instruction. If CX = 0, after the auto decrement or if ZF = 1, execution simply go on the next instruction after LOOPNE / LOOPNZ.

MOV BX, [4000] Point BX to adjust before start of array

DEC BX Decrement BX

MOV CX, 100

Put number of array in CX

NEXT: INC BX

Point to next element in array

CMP [RX] ODH

Compare array element with ODH

CMP [BX], ODH Compare array element with 0DH LOOPNZ NEXT

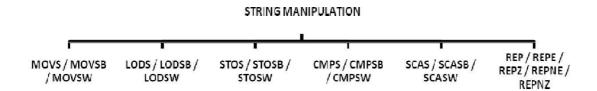

#### g. STRING MANIPULATION INSTRUCTIONS

#### MOVS / MOVSB / MOVSW

This instruction copies a byte or a word from location in the data segment to a location in the extra segment. The offset of the source in the data segment must be in the SI register. The offset of the destination in the extra segment must be in the DI register. For multiple-byte or multiple-word moves, the number of elements to be moved is put in the CX register so that it can function as a counter. After the byte or a word is moved, SI and DI are automatically adjusted to point to the next source element and the next destination element. If DF is 0, then SI and DI will be incremented by 1 after a byte move and by 2 after a word move. If DF is 1, then SI and DI will be decremented by 1 after a byte move and by 2 after a word move.

| MOV SI, 5000 | Load 5000 into SI                               |

|--------------|-------------------------------------------------|

| MOV DI, 6000 | Load 6000 into DI                               |

| CLD          | Clear DF to auto increment SI and DI after move |

| MOV CX, 04H  | Load length of string into CX as counter        |

| REP MOVSB    |                                                 |

| KEP MOVSD    | Move string byte until $CX = 0$                 |

## LODS / LODSB / LODSW (LOAD STRING BYTE INTO AL OR STRING WORD INTO AX)

This instruction copies a byte from a string location pointed to by SI to AL, or a word from a string location pointed to by SI to AX. If DF is 0, SI will be automatically incremented (by 1 for a byte string, and 2 for a word string) to point to the next element of the string. If DF is 1, SI will be automatically decremented (by 1 for a byte string, and 2 for a word string) to point to the previous element of the string. LODS does not affect any flag.

CLD Clear direction flag so that SI is auto-incremented

MOV SI, OFFSET SOURCE Point SI to start of string

LODS SOURCE Copy a byte or a word from string to AL or AX

#### STOS / STOSB / STOSW (STORE STRING BYTE OR STRING WORD)

This instruction copies a byte from AL or a word from AX to a memory location in the extra segment pointed to by DI. In effect, it replaces a string element with a byte from AL or a word from AX. After the copy, DI is automatically incremented or decremented to point to next or previous element of the string. If DF is cleared, then DI will automatically incremented by 1 for a byte string and by 2 for a word string. If DI is set, DI will be automatically decremented by 1 for a byte string and by 2 for a word string.

MOV DI, OFFSET TARGET STOS TARGET

#### CMPS / CMPSB / CMPSW (COMPARE STRING BYTES OR STRING WORDS)

This instruction can be used to compare a byte / word in one string with a byte / word in another string. SI is used to hold the offset of the byte or word in the source string, and DI is used to hold the offset of the byte or word in the destination string. The AF, CF, OF, PF, SF, and ZF flags are affected by the comparison, but the two operands are not affected.

After the comparison, SI and DI will automatically be incremented or decremented to point to the next or previous element in the two strings. If DF is set, then SI and DI will automatically be decremented by 1 for a byte string and by 2 for a word string. If DF is reset, then SI and DI will automatically be incremented by 1 for byte strings and by 2 for word strings. The string pointed to by SI must be in the data segment. The string pointed to by DI must be in the extra segment.

The CMPS instruction can be used with a REPE or REPNE prefix to compare all the elements of a string.

| MOV SI, 5000 | Point SI to 5000                                          |

|--------------|-----------------------------------------------------------|

| MOV DI, 6000 | Point DI to 6000                                          |

| CLD          | DF cleared, SI and DI will auto-increment after compare   |

| MOV CX, 100  | Put number of string elements in CX                       |

| REPE CMPSB   | Repeat the comparison of string bytes until end of string |

|              | or until compared bytes are not equal                     |

CX functions as a counter, which the REPE prefix will cause CX to be decremented after each compare. The B attached to CMPS tells the assembler that the strings are of type byte. If you want to tell the assembler that strings are of type word, write the instruction as CMPSW. The REPE CMPSW instruction will cause the pointers in SI and DI to be incremented by 2 after each compare, if the direction flag is set.

#### SCAS / SCASB / SCASW (SCAN A STRING BYTE OR A STRING WORD)

SCAS compares a byte in AL or a word in AX with a byte or a word in ES pointed to by DI. Therefore, the string to be scanned must be in the extra segment, and DI must contain the offset of the byte or the word to be compared. If DF is cleared, then DI will be incremented by 1 for byte strings and by 2 for word strings. If DF is set, then DI will be decremented by 1 for byte strings and by 2 for word strings. SCAS affects AF, CF, OF, PF, SF, and ZF, but it does not change either the operand in AL (AX) or the operand in the string. The following program segment scans a text string of 80 characters for a carriage return, 0DH, and puts the offset of string into DI:

MOV DI, OFFSET STRING

MOV AL, 0DH

Byte to be scanned for into AL

CX used as element counter

CLD

Clear DF, so that DI auto increments

REPNE SCAS STRING

Compare byte in string with byte in AL

#### REP / REPE / REPZ / REPNE / REPNZ (PREFIX)

#### (REPEAT STRING INSTRUCTION UNTIL SPECIFIED CONDITIONS EXIST)

REP is a prefix, which is written before one of the string instructions. It will cause the CX register to be decremented and the string instruction to be repeated until CX = 0. The instruction REP MOVSB, for example, will continue to copy string bytes until the number of bytes loaded into CX has been copied.

REPE and REPZ are two mnemonics for the same prefix. They stand for *repeat if equal* and *repeat if zero*, respectively. They are often used with the Compare String instruction or with the Scan String instruction. They will cause the string instruction to be repeated as long as the compared bytes or words are equal (ZF = 1) and CX is not yet counted down to zero. In other words, there are two conditions that will stop the repetition: CX = 0 or string bytes or words not equal.

REPE CMPSB Compare string bytes until end of string or until string bytes not equal

REPNE and REPNZ are also two mnemonics for the same prefix. They stand for *repeat if not equal* and *repeat if not zero*, respectively. They are often used with the Compare String instruction or with the Scan String instruction. They will cause the string instruction to be repeated as long as the compared bytes or words are not equal (ZF = 0) and CX is not yet counted down to zero.

REPNE SCASW

Scan a string of word until a word in the string matches the word in AX or until all of the string has been scanned.

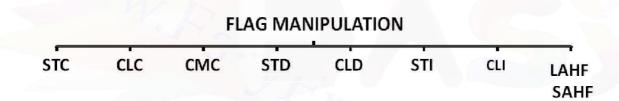

#### h. FLAG MANIPULATION INSTRUCTIONS

**STC (SET CARRY FLAG)** sets the carry flag to 1.

**CLC** (**CLEAR CARRY FLAG**) resets the carry flag to 0.

CMC (COMPLEMENT CARRY FLAG) complements the carry flag.

**STD** (**SET DIRECTION FLAG**) sets the direction flag to 1.

**CLD (CLEAR DIRECTION FLAG)** resets the direction flag to 0

**STI** (**SET INTERRUPT FLAG**) Setting the interrupt flag to a 1 enables the INTR interrupt input

**CLI (CLEAR INTERRUPT FLAG)** resets the interrupt flag to 0.

#### LAHF (COPY LOW BYTE OF FLAG REGISTER TO AH REGISTER)

The LAHF instruction copies the low-byte of the 8086 flag register to AH register.

#### SAHF (COPY AH REGISTER TO LOW BYTE OF FLAG REGISTER)

The SAHF instruction replaces the low-byte of the 8086 flag register with a byte from the AH register.

#### i. STACK RELATED INSTRUCTIONS

#### **PUSH – PUSH Source**

The PUSH instruction decrements the stack pointer by 2 and copies a word from a specified source to the location in the stack segment to which the stack pointer points.

**PUSH BX**

Decrement SP by 2, copy BX to stack.

#### **POP – POP Destination**

The POP instruction copies a word from the stack location pointed to by the stack pointer to a destination specified in the instruction. After the word is copied to the specified destination, the stack pointer is automatically incremented by 2 to point to the next word on the stack

POP DX Copy a word from top of stack to DX; increment SP by 2

#### PUSHF (PUSH FLAG REGISTER TO STACK)

The PUSHF instruction decrements the stack pointer by 2 and copies a word in the flag register to two memory locations in stack pointed to by the stack pointer.

#### POPF (POP WORD FROM TOP OF STACK TO FLAG REGISTER)

The POPF instruction copies a word from two memory locations at the top of the stack to the flag register and increments the stack pointer by 2.

#### j. INPUT-OUTPUT INSTRUCTIONS

#### IN - IN Accumulator, Port

The IN instruction copies data from a port to the AL or AX register. If an 8-bit port is read, the data will go to AL. If a 16-bit port is read, the data will go to AX.

IN AX, 34H Input a word from port 34H to AX

For the variable-port form of the IN instruction, the port address is loaded into the DX register before the IN instruction. Since DX is a 16-bit register, the port address can be any number between 0000H and FFFFH. Therefore, up to 65,536 ports are addressable in this mode.

MOV DX, 0FF78H Initialize DX to point to port

IN AL, DX Input a byte from 8-bit port 0FF78H to AL

#### **OUT - OUT Port, Accumulator**

The OUT instruction copies a byte from AL or a word from AX to the specified port. The OUT instruction has two possible forms, fixed port and variable port. For the fixed port form, the 8-bit port address is specified directly in the instruction. With this form, any one of 256 possible ports can be addressed.